隨著摩爾時代持續推進,摩爾定律逐步逼近物理極限。晶片尺寸不斷縮小,製程節點已從奈米邁向埃米等級;隨著電晶體密度持續提高、堆疊層數不斷增加,傳統 2D 晶片架構逐漸逼近極限,製程也正加速朝 3D 化發展。在此架構演進下,過去並非核心問題的「供電」開始浮上檯面,成為限制製程持續微縮的關鍵瓶頸之一。一方面,電源佈線佔據大量晶片正面空間,壓縮邏輯電路的布局彈性;另一方面,電力在傳輸過程中產生的 IR drop 與能量損耗,也直接限制效能與能效表現。

因此,晶片供電逐漸從輔助設計,轉變為延續摩爾定律的重要工具。主要三大晶圓代工廠——台積電、三星與英特爾——皆陸續提出「晶背供電」(BSPDN, Backside Power Delivery Network)技術,透過將供電網路移至晶片背面,改善供電效率,同時釋放晶片正面空間,以承載更多高密度邏輯電路。 本文將聚焦於台積電的晶背供電技術發展。根據目前規劃,台積電預計於2026 年第三季A16 製程中導入 BSPDN,並將其視為先進製程節點中不可或缺的關鍵技術之一。

技術背景:晶片微縮進程面臨的挑戰

目前晶片微縮所面臨的核心挑戰,主要可歸結為兩大問題:其一是可用佈線空間持續壓縮,其二是效能提升逐漸遭遇結構性的瓶頸。 在傳統邏輯晶片架構中,晶片通常由基板、電晶體層,以及位於最上方的多層金屬佈線層所構成。隨著製程節點不斷推進,在既有供電與佈線架構未出現根本性改變的情況下,這兩項限制被進一步放大,成為制約技術演進的關鍵因素。

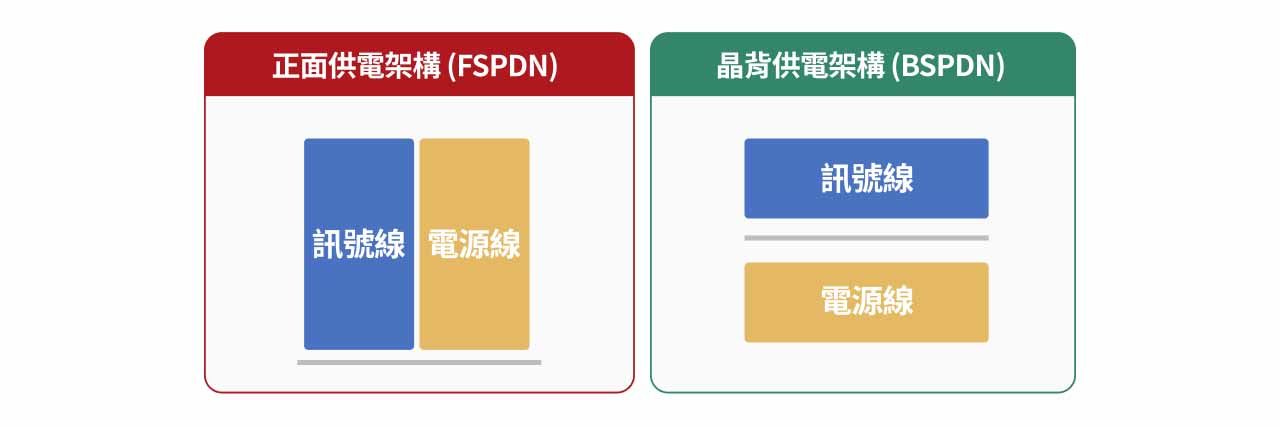

現行主流採用的是正面供電架構(FSPDN)。 電流由晶圓正面引入,必須穿越約 60~70 層金屬佈線,才能一路傳遞至最底層的電晶體。簡單來說,就像是從一棟 70 層的大樓頂樓拉電線,一路拉到一樓;隨著製程持續微縮、線寬變窄,導線電阻不斷上升,壓降(IR Drop)問題也隨之惡化,同時帶來更高的功耗與干擾風險,逐漸成為效能提升的瓶頸。

在金屬佈線結構中,依功能大致可分為兩類路徑: 一類是訊號線,負責傳輸邏輯訊號,電壓與電流相對微弱,但路徑複雜且數量龐大; 另一類則是電源線,主要任務是將外部電流導入電晶體,提供其開關所需的能量。

然而,在傳統正面供電架構下,電源線必須與大量訊號線共用有限的正面佈線空間。當製程持續微縮、金屬層數增加時,這種空間競爭便具體表現在以下幾個工程層面的問題上:

- 隨著線寬縮小,導線電阻上升,使壓降(IR Drop)持續惡化

- 底層電晶體實際可取得的電壓不足,能量損失限制其效能發揮

- 電源線與訊號線距離過近,電磁干擾加劇,進一步推升功耗與設計複雜度

技術介紹:晶背供電是什麼?

晶背供電是將原先配置於晶片正面的電源供應路徑移轉至晶片背面,藉此釋放正面同時承載訊號線與電源線所占用的佈線空間。

晶背供電的核心主要建立在兩項關鍵技術之上:埋入式電源軌(Buried Power Rail, BPR)以及奈米矽穿孔(Nano Through-Silicon Via, n-TSV)。

- 埋入式電源軌: 是將垂直方向的電源線(VDD、VSS)直接嵌入基板內部,使供電路徑不再佔用晶片正面的金屬佈線層,並與後段製程(Back End of Line, BEOL)中負責訊號傳輸的金屬線路完全分離。這樣的設計,等於在結構上將「供電」與「訊號」兩套系統拆開處理,避免彼此爭奪有限的佈線空間。

- 奈米矽穿孔: 是在基板中垂直鑽設高密度、奈米尺度的通孔,並於孔內填充導電材料,形成由晶片背面直達電晶體層的垂直導電通道。透過這些奈米矽穿孔(n-TSV),電源與接地可以直接由基板背面導入,大幅縮短供電路徑,並有效降低電阻與壓降。

綜合而言,BPR 負責在基板內建立穩定的電源骨幹,而 n-TSV 則扮演連接背面供電與前端電晶體的關鍵橋樑,使得「從背面供電」在先進邏輯製程中具備實際可行性。

台積電 Super Power Rail 晶背供電技術

與英特爾先導入的 PowerVia 晶背供電技術 不同,台積電的晶背供電技術為 Super Power Rail (SPR),台積電採用 Back-to Back,直接利用晶背供電其中也是目前現有三種中最複雜的。

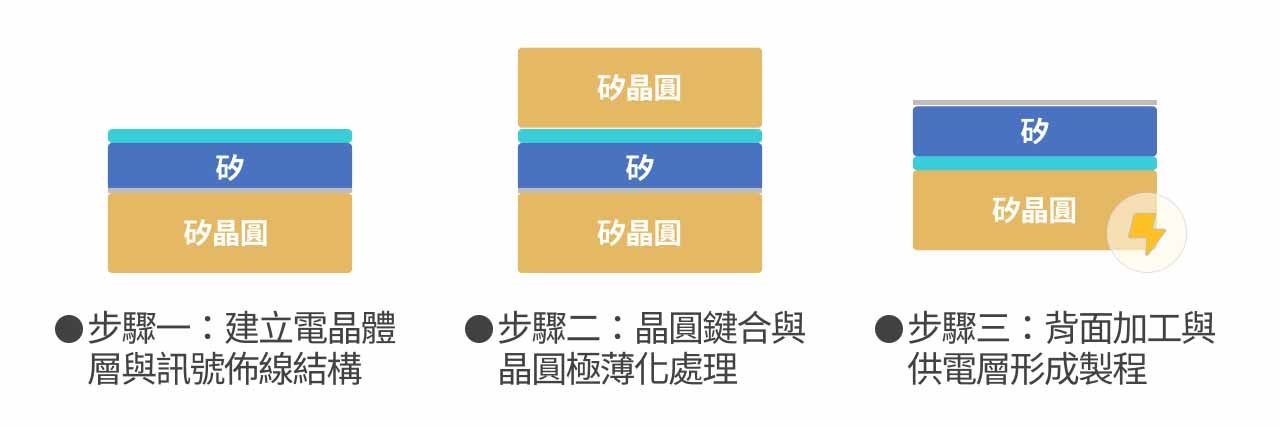

步驟一:建立電晶體層與訊號佈線結構

製程首先以一片厚度約 600,000 奈米(600 µm) 的矽晶圓作為基底,在其上方建構約 100 奈米 厚度的電晶體層,並進一步堆疊約 500 奈米 厚度的訊號導線區。 與傳統製程不同的是,此階段僅需構築訊號導線,而不再同時建立電源線,因為在晶背供電架構中,電源分配網路將改由晶圓背面實現,使前段金屬層能專注於訊號傳輸功能。

步驟二:晶圓鍵合與晶圓極薄化處理

當訊號線區完成後,需將整片晶圓與另一片同樣厚度約 600,000 奈米 的矽晶圓進行 Wafer Bonding,上方晶圓即作為承載晶圓(Carrier Wafer)。 此步驟的目的在於,為後續背面加工與極端薄化提供必要的機械支撐。由於原始晶圓本體將從 600 µm 大幅削薄,最終僅剩電晶體層,整體結構幾乎喪失剛性,若缺乏外部支撐,將無法承受設備夾持、搬運以及後段製程所產生的熱與機械應力。

步驟三:背面加工與供電層形成製程

完成鍵合後,晶圓進入研磨與化學機械平坦化(CMP)階段,將原始矽基底完全去除,只保留前段製程所形成的電晶體層,此時晶圓已翻轉,使原本的背面朝上。 接著透過矽穿孔技術,在電晶體底部開孔以建立背面供電通道,並於其上沉積約 500 奈米 厚度的電源金屬層,最終完成晶背供電層的建構。

晶背供電中的關鍵步驟:晶圓薄化與再生晶圓應用

在晶背供電與先進封裝製程中,晶圓薄化是不可或缺的關鍵步驟。由於晶片電路皆製作於晶圓正面,前段製程必須使用具備足夠厚度與結構強度的晶圓,以承受高溫與多道製程要求;然而,當電路製作完成後,若晶圓維持過厚,將限制後續背面供電佈線、散熱效率與封裝堆疊設計。因此,實務上需於主要製程完成後,自晶圓背面進行極度薄化,以滿足晶背供電與先進封裝對厚度與結構配置的要求。

然而,晶圓在薄化後結構極為脆弱,已無法承受後續製程與搬運需求,使晶圓鍵合成為必要前置步驟。透過暫時鍵合,將製程晶圓固定於承載晶圓上,可提供必要的機械支撐,確保薄化與背面製程的穩定性與良率。

在此流程中,再生晶圓同時被廣泛應用於承載晶圓與製程測試晶圓。 一方面,承載晶圓不需具備產品功能,只需滿足平整度與結構強度要求,再生晶圓即可勝任並可重複使用;另一方面,鍵合、薄化與背面製程導入前後,需大量進行製程驗證與設備校正,測試晶圓用量大幅增加,使用再生晶圓有助於有效控制成本。

整體而言,晶圓薄化決定先進製程與晶背供電的可行性,晶圓鍵合確保製程穩定,而再生晶圓則支撐其量產與成本結構,三者相互依存、缺一不可。

再生晶圓

再生晶圓(Reclaimed Wafer)是指將曾投入半導體製程、但結構仍完整的矽晶圓,經由去膜、研磨、CMP 拋光與缺陷檢測等程序重新加工後,再次用於製程監控、測試或假片用途。 由於不直接作為最終產品晶片,其成本明顯低於原生晶圓,卻能滿足晶圓廠在製程穩定性與設備校準上的需求。

在晶背供電製程中,再生晶圓常被應用於承載晶圓,當元件晶圓因電性連接需求進行背磨,厚度降至約 100 微米,甚至進一步薄化至 10 微米以下時,晶圓的機械強度將顯著下降,於搬運或高溫製程過程中容易產生破片或嚴重翹曲。此時,承載晶圓的核心功能在於提供穩定且可靠的支撐基板,使超薄元件晶圓得以維持結構完整性,並順利完成後續微影、金屬沉積、CMP 與乾式蝕刻等製程,同時降低因晶圓破裂或翹曲所造成的良率損失。整體而言,在先進封裝與高階 AI 晶片製造中,承載技術的成熟度已直接影響整體製造成本、良率表現與產品穩定性。

製造流程

1. 分類(Sort) 此步驟的主要目的,是在再生製程開始前,先篩選不適合的晶圓,避免金屬汙染進入再生產線。所有進料晶圓皆會逐片檢查,包含外觀是否有缺陷、晶圓種類,以及基本的材料與結構特性。檢查結果將用來判斷晶圓是否適合再生,並決定後續應採用的再生製程流程。

2. 去膜(Strip) 去膜的目的是將晶圓表面原有的各類薄膜移除,讓晶圓能順利進入後續的再生製程。 實際採用的去膜方式,會依晶圓的來料狀況進行調整,通常於自動化的濕式批次清洗設備中完成。常見使用的處理藥液包含 SPM(硫酸+過氧化氫)、高濃度 HF 蝕刻,以及 鹼性蝕刻(如 KOH),並依不同薄膜類型選擇搭配使用。若晶圓表面含有金屬薄膜,則需增加額外的前處理步驟。此階段最重要的重點,在於確保薄膜完整去除,同時避免不同晶圓之間發生交叉汙染。

3. 研磨與修邊(Grinding & Edge Treatment) 對於中間含有絕緣層、結構較厚的 SOI 晶圓,或需移除特定薄膜的情況,通常會先進行研磨製程,並同時搭配修邊與邊角圓化處理,以改善晶圓外型與製程穩定性。 研磨的優點是材料去除速度快,但在厚度與表面均勻性上較難控制,因此在研磨完成後,會再透過 CMP 進行平滑處理與最終拋光,以提升表面品質並確保晶圓平整度,使其符合後續製程需求。

4. 拋光(Polish) 拋光可分為單面或雙面拋光,通常結合化學與機械方式進行。其中,雙面拋光可有效降低 TTV(總厚度變異),使晶圓厚度更為一致。 完成拋光後,晶圓表面會回到裸矽狀態,整體厚度也會低於原始晶圓,並可進入最終清洗階段。不過拋光過程中,表面可能殘留拋光漿料、微粒或金屬汙染,因此必須在後續清洗製程中徹底去除。

5. 清洗(Clean) 最終清洗通常在自動化批次濕式清洗設備中完成,並可於同一套設備中依序進行多個清洗步驟。 清洗流程採用標準 RCA 清洗,包含: SC-1(H₂O/NH₄OH/H₂O₂):用於移除晶圓表面的粒子與殘留物 SC-2(H₂O/HCl/H₂O₂):用於降低金屬汙染 經過清洗後,晶圓表面的金屬濃度可降至 5×10¹⁰ atoms/cm² 以下,實務上通常可達 1×10¹⁰ 以下。最後再透過表面張力乾燥完成整個清洗流程。

6. 檢測(Inspection) 再生完成後,晶圓會依厚度與表面缺陷數進行分類與分級。一般測試晶圓需符合 0.12 µm LPD(Light Point Defect,光點缺陷)小於 50 顆的典型規格。

由於測試晶圓常被用於設備調校與製程問題排查,其缺陷表現會直接影響判斷結果,因此缺陷控制是再生製程中相當關鍵的一環。

再生晶圓的優勢

- 降低生產成本:再生晶圓的使用成本約為新晶圓的 20–30%,可有效降低測試與非關鍵製程的整體支出

- 減碳與永續:相較於新晶圓製造,再生流程在能耗與用水量上可減少約 60–80%,符合半導體產業的減碳與 ESG 發展方向

- 提升製程穩定與良率:透過大量再生晶圓進行設備驗證與製程測試,有助於提前發現製程偏移,降低量產風險

先進製程推升再生晶圓需求

隨著製程節點持續微縮,再生晶圓的需求明顯放大。昇陽半導體在法說會中指出:

- 5 奈米製程:投片 10 萬片,約需 10 萬片再生晶圓

- 3 奈米製程:再生晶圓需求提升至約 2.2 倍

- 2 奈米製程:再生晶圓需求進一步拉高至 2.6 倍以上

這代表製程愈先進,對測試、校正與製程控制的依賴程度愈高,再生晶圓已不再只是輔助材料,而是支撐先進製程運作的重要基礎資源。 再生晶圓原本只是前段製程中的測試耗材,但隨著製程節點持續推進與先進封裝需求提升,其角色已轉變為支撐製程穩定、降低成本,並支援超薄元件晶圓製造的重要基礎材料。

再生晶圓原本只是前段製程中的測試耗材,但隨著製程節點持續推進與先進封裝需求提升,其角色已轉變為支撐製程穩定、降低成本,並支援超薄元件晶圓製造的重要基礎材料。

晶圓薄化

晶圓薄化(Wafer Thinning)是指在半導體製造流程中,於前段製程完成後,從晶圓的背面移除材料,使晶圓整體厚度降低。 這個步驟的目的在於因應晶片小型化與先進封裝需求,讓晶片能夠做到更薄、更小,並支援堆疊與高密度整合,進而應用於體積受限但效能要求更高的電子產品。

晶圓薄化的優勢

晶圓薄化不只是為了變薄,而是直接影響整體封裝與效能表現,主要效益包括:

- 散熱表現提升:晶片變薄後,熱較容易傳導,有助於高效能晶片長時間運作的穩定性

- 封裝尺寸縮小:較薄的晶片可支援更高密度的封裝與堆疊,有利於裝置小型化

- 降低內部應力:厚晶片在溫度變化下容易累積內部應力,薄化後可降低裂損風險

- 電性表現改善:結構距離縮短,有助於提升高頻訊號與整體電性效率

- 切割與封裝良率提升:薄化後的晶圓較不易在切割與封裝過程中產生崩邊或損傷

晶圓薄化的限制

由於積體電路製作於晶圓正面,晶圓於前段製程階段需維持高度的平整度與結構穩定性,因此晶圓薄化僅能於主要製程完成後進行,並透過背面逐步移除材料的方式達成目標厚度。 在此過程中,晶圓平整度的控制成為影響製程良率的關鍵因素。

隨製程節點持續微縮,晶圓薄化對背面研磨均勻性與平坦度的要求大幅提高,使化學機械平坦化製程的重要性進一步提升。其中,鑽石碟作為研磨墊修整的核心耗材,直接決定研磨條件的穩定性與一致性,其精度與耐用度將影響晶圓薄化品質與最終製程良率,在先進製程中扮演不可替代的關鍵角色。

常見的晶圓薄化方式

實務上,晶圓薄化並非只依賴單一方法,而是依製程需求進行搭配使用,常見方式包括:

- 機械研磨:最常見的薄化手段,透過研磨設備快速去除背面材料,通常分為粗磨與細磨

- 化學機械研磨(CMP):在研磨過程中搭配化學藥液,改善表面平坦度與品質,但成本與製程要求較高

- 化學蝕刻:利用化學方式進一步移除材料,常作為研磨後的表面修整

- 電漿相關技術:透過電漿與化學反應進行薄化,特色是厚度均勻性較佳,常用於先進製程

在台積電的晶背供電技術中主要用到機械研磨和化學機械研磨。

晶圓薄化的核心概念在於先以較厚的晶圓完成電路製作,再從背面進行薄化,以同時兼顧製程穩定性與最終產品對小型化、散熱與先進封裝的需求。隨著先進封裝與高效能晶片發展,晶圓薄化已成為不可或缺的關鍵製程之一。

晶背供電技術比較:台積電 vs. Intel vs. Samsung

![台積電、三星、英特爾logo圖。]

競爭格局呈現三強鼎立,除了台積電使用晶背供電技術以外,英特爾試圖透過率先量產來重奪技術領導地位,三星則緊隨其後,預計於 2027 年量產。雖然晶背供電的總體目標一致,但各家廠商在具體實作路徑上存在顯著差異,主要體現在電源接入點(Tap Point)與製造流程的複雜度上。

技術導入進度

英特爾 PowerVia 的商用化進度

英特爾的 PowerVia 是其 Intel 18A 製程的關鍵組成,與 RibbonFET(GAA)同步導入,目標在於透過背面供電降低 IR drop 並釋放前端佈線資源。 英特爾於 2026 年 CES 正式發布 Core Ultra Series 3(Panther Lake),該系列為首批採用 18A 製程的客戶端處理器,象徵 PowerVia 從研發階段邁入實際商用產品週期。

就製程成熟度而言,18A 目前仍處於量產爬坡階段。英特爾管理層指出,現階段良率已可支撐產品出貨,但距離理想的成本結構仍有差距,顯示背面供電相關製程仍是成本與良率管理的挑戰。 所以PowerVia 已進入可商用階段,但其長期經濟性與對 PPA 的全面影響,仍有待更多量產數據驗證。策略層面,Intel 18A 與 PowerVia 亦被視為其晶圓代工服務的重要差異化技術。雖然外部客戶的實際量產案例尚未公開,但美國本土製造的特性,使其在供應鏈安全與政策導向應用上具備一定戰略價值。

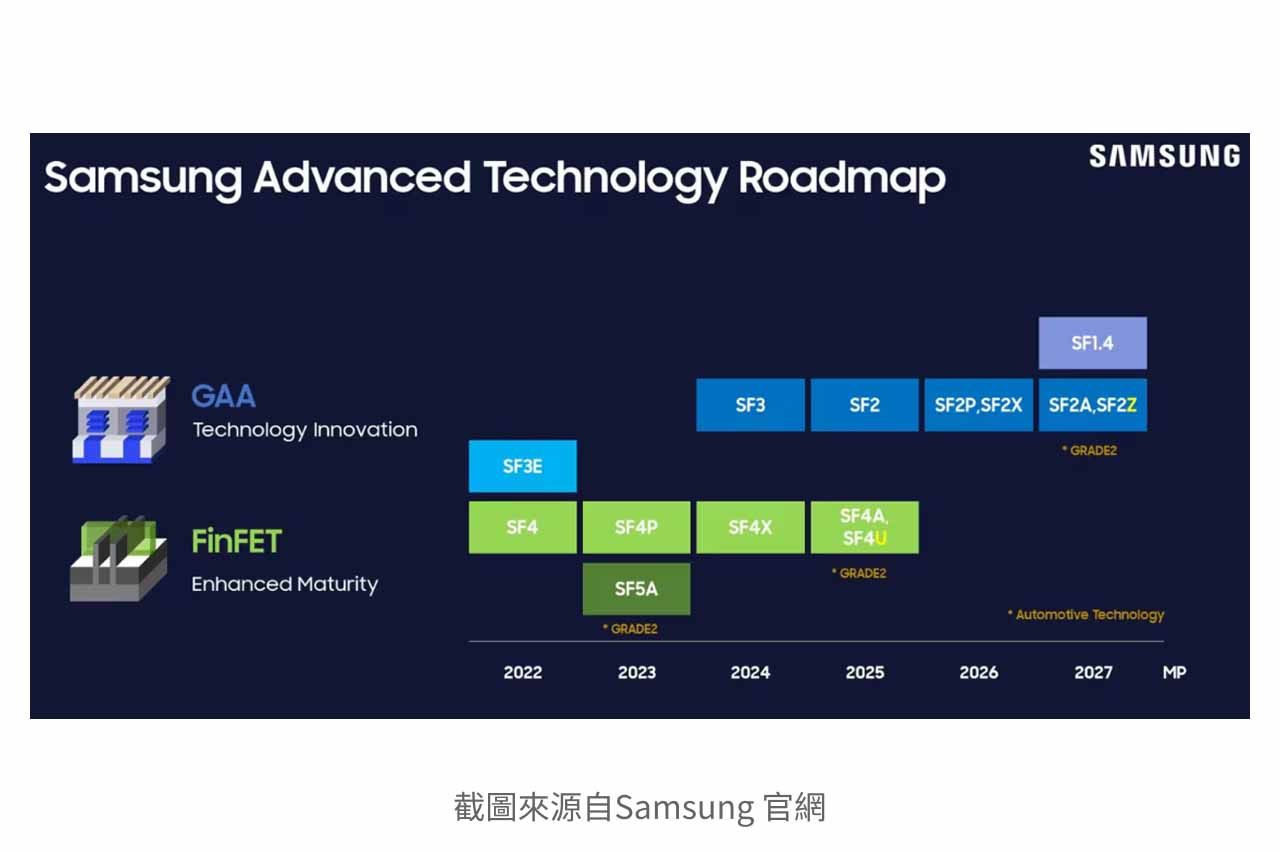

三星 SF2Z 的未來佈局

三星的 SF2Z 為 2 奈米製程家族中整合背面供電的進階版本,主要鎖定 HPC 與 AI 應用,量產時程預計落在 2027 年。 SF2Z 建構於三星已量產多代的 MBCFET(GAA) 架構之上,延續其在奈米片電晶體上的製程經驗。

SF2Z 的核心目標在於,透過背面供電改善高功率密度設計下的供電瓶頸,進一步提升整體 PPA 表現。不過,截至目前為止,三星尚未公開具體的效能或功耗改善數據,其實際效益仍有待量產後驗證。相較競爭對手,SF2Z 的主要風險在於導入時間較晚,能否以足夠的 PPA 優勢與良率表現彌補時程落後,將是其市場競爭力的關鍵。

Intel PowerVia 製造流程的關鍵差異

Intel 為最早導入晶背供電技術的廠商,而台積電在技術路線上,則與 Intel 展現出多項顯著差異:

PowerVia 在前段製程預埋 Nano-TSV

與台積電 Super Power Rail 由背面直接建立電源接觸不同,Intel PowerVia 的核心設計在於前段製程即同步預埋 Nano-TSV(奈米級矽穿孔)。 這些 Nano-TSV 在電晶體製作階段便已形成,但初期僅為「盲孔」結構,尚未貫穿晶圓。此作法與封裝層級 TSV 明顯不同,其奈米級尺寸與電晶體同步對位的特性,使電源垂直連接能在極小面積內完成,避免侵蝕標準單元佈局空間。相較之下,台積電 Super Power Rail 並未採用 TSV 類結構,而是以背面金屬層直接連接電晶體端點,兩者在電源垂直導通路徑上屬於不同工程哲學。

PowerVia 將電源完全移至晶圓背面,使正面金屬層專注於訊號傳輸

在 PowerVia 架構下,Intel 將電源與接地路徑完全移至晶圓背面,使正面所有金屬層得以專注於訊號傳輸。這一點與台積電仍需在正面層次中保留部分供電結構的作法不同。 PowerVia 因此在正面獲得更高的訊號佈線自由度,能有效降低繞線、串擾與 RC 延遲,這也是 Intel 強調其在邏輯密度與時脈提升上的重要基礎。

PowerVia 的關鍵風險在於薄化過程中需精準露出預埋的 Nano-TSV

Intel PowerVia 同樣需要經歷晶圓翻轉、鍵合至載體晶圓並進行極致減薄,但其風險集中點與台積電不同。由於 Nano-TSV 早已預埋於晶圓內部,減薄工程的關鍵在於精準停止於 TSV 頂端,確保 TSV 能被完整露出而不受損。 此步驟對厚度控制與翹曲管理的要求極高,也使 PowerVia 的良率與成本高度取決於鍵合與研磨精度。而台積電 Super Power Rail 面臨的挑戰更多在於背面對準與直接接觸源極/汲極的製程控制,兩者風險結構並不相同。

PowerVia 採用三段式供電架構

在晶圓背面,Intel 建立專屬的粗線寬背面電源網路,並透過 Nano-TSV 將電力垂直傳輸至電晶體接觸層。此一「背面電源 → TSV → 電晶體」的三段式結構,是 PowerVia 的核心特徵,也與台積電採取「背面金屬直接接觸電晶體端點」的設計形成鮮明對比。 PowerVia 的優勢在於 TSV 提供高度可控的垂直導通路徑,而代價則是額外的製程步驟與結構複雜度。

晶背供電技術綜合比較

在背面供電逐步走向量產落地的過程中,台積電、Intel 與 Samsung 已分別選擇不同的實現路徑,反映其在製程整合能力、風險承受度與產品節點策略上的差異。

- Intel 率先於 18A 節點導入 PowerVia,強調設計連續性與量產可行性

- Samsung 則在 GAA 架構下結合背面供電與既有埋入式電軌設計,試圖在密度與效能間取得平衡

- 台積電的 A16 Super Power Rail 則被視為最具前瞻性的方案,潛在微縮效益最高,但同時伴隨較高的製程複雜度與量產挑戰。

以下比較表從量產時程、電晶體與供電架構、連接機制,以及效能與風險面向,對三家先進節點的晶背供電策略進行對照,藉此評估各大廠在下一世代先進製程競爭中的技術定位。

| 比較項目 | Super Power Rail | PowerVia | BSPDN |

|---|---|---|---|

| 公司 | 台積電(TSMC) | 英特爾(Intel) | 三星(Samsung) |

| 量產時間 | 2026 年下半年(2H26) | 2025 年下半年(2H25) | 2027 年 |

| 效能表現 | 1. 在相同電壓下,時脈提升約 10% 2. 在相同頻率與電路複雜度下,功耗降低約 15%–20% 3. 電晶體密度提升約 7%–10% | 1. 晶片多數區域的標準單元利用率可超過 90% 2. 平台電壓下陷(Voltage Droop)改善約 30% 3. 頻率提升約 6% | 1. 晶圓面積使用率降低約 14.8% 2. 佈線長度縮短約 9.2%,有助於降低電阻、提升電流傳輸能力 |

| 技術特點 | 1. 導入於 A16 製程,並與 GAA 電晶體架構結合 2. 將電源傳輸線直接連接至電晶體源極/汲極(S/D),顯著提升晶片供電效率 | 1. 導入於 18A 製程,並與 RibbonFET 架構結合 2. 透過 nanoTSV 將背面供電網路連接至電晶體接觸層 | 導入於 SF2Z 製程,並與 GAA(MBCFET)架構結合 |

技術影響:晶背供電帶來供應鏈重塑

晶背供電技術的導入,對於台積電所處的全球半導體產業群體而言,不僅是一項製程突破,更可能重塑未來幾年的市場結構與供應鏈配置。全球半導體市場正處於由 AI 需求主導的高速成長階段,其中先進邏輯製程與高價 HBM 記憶體等高階產品的需求是主要動能來源。這代表對超高性能晶片設計與製造的壓力將持續上升,而背面供電等前沿架構技術正好對應這一需求環境。

從市場定位層面看,台積電在 A16 導入 Super Power Rail 等 BSPDN 架構,是因應 AI 加速器、HPC 平台與雲端資料中心日益複雜的供電與能效要求,而非單純追逐摩爾定律的線寬縮減。這一策略能在未來產品組合中向客戶提供更佳的能效比與電源完整性設計空間,尤其是面對內建大規模運算與高帶寬記憶體的晶片設計,SPR 的潛在價值不僅在於提升單顆晶片效能,更在於支撐市場對高階應用的設計需求。

從供應鏈影響來看,晶背供電的廣泛應用可能帶動產業上下游結構性升級。 一方面,先進製程設備與材料需求將同步提升,涉及晶圓減薄、背面鍵合、高精度製程檢測與先進封裝等領域的廠商可能因技術門檻提高而獲益。晶背供電與再生晶圓技術正推動製程材料與設備市場的需求加速,包括研磨耗材、乘載晶圓等高精密耗材的應用價值提升。這意味著台積電的技術選擇不僅影響自身製造平台,也會透過供應鏈擴展帶動相關產業的增量成長。

此外在全球供應鏈競爭與市場需求多元化的背景下,台積電在最先進製程持續領先,可強化其在高階邏輯與 AI 晶片生產中的龍頭地位,進一步凝聚客戶陣營。 由於不同應用市場對 PPA 與可靠性要求顯著提高,先進背面供電技術有望成為晶片設計不可或缺的一環,而能夠提供高效能製程平台的代工廠將更具價格與議價空間。這種市場驅動下的技術導入,不僅強化台積電作為全球 Fab 1 角色的競爭優勢,也可能促進其更緊密地參與全球高階應用生態系整合。

綜觀整體產業趨勢,在 AI 與 HPC 推升需求、先進製程占比提升的背景下,晶背供電等技術的落地將從系統需求端、供應鏈結構與製造競爭力共同推動市場格局變化,台積電若能在此領域持續保持技術與量產優勢,其市場定位與長期營收結構有望進一步穩固與提升。

晶背供電技術受惠台廠

中砂(1560.TW)

中砂為半導體製程中 CMP 相關耗材的重要供應商,專注先進製程所需之精密研磨與平坦化耗材,產品涵蓋鑽石碟、砂輪及再生晶圓,主要應用於台積電等一線晶圓代工廠。 公司由傳統砂輪起家,隨取得鑽石碟關鍵技術並配合台積電供應鏈在地化策略,成功轉型為具研磨與切割核心能力的精密耗材製造商。其競爭優勢在於鑽石碟為 CMP 製程關鍵耗材、替代性低且具高認證門檻,並與台積電長期深度合作,於 3 奈米製程市佔率約七成,同時具備鑽石碟與再生晶圓的材料整合能力。

在 BSPDN 發展趨勢下,中砂可望受惠於:

- 鑽石碟需求具高度剛性,隨 2 奈米製程量產推進,對平整度要求提升,月出貨量已突破 5 萬顆

- 先進製程研發帶動再生晶圓需求,隨製程驗證與設備校正需求增加,挹注穩定成長動能。

整體而言,中砂在台積電供應鏈中具備高市占的鑽石碟關鍵地位,並同時擁有再生晶圓製造優勢,隨先進製程推進,為台積電先進製程相關需求下的核心受益者之一。

昇陽半導體(8028.TW)

昇陽半導體為台灣長期深耕再生晶圓與晶圓薄化製程的晶圓材料提供商,專注於服務先進製程與高階製造需求。 公司核心業務涵蓋再生晶圓供應、晶圓薄化及相關材料處理技術,主要客戶包含台積電等一線晶圓代工廠。其競爭優勢主要來自與台積電長期合作所累積的製程理解與客戶黏著度,以及在再生晶圓領域具備高度市占率與規模化量產能力。

在 BSPDN 技術發展趨勢下,昇陽半導體可望受惠於:

- 先進製程持續推進,設備校正與製程測試需求提升,帶動再生晶圓使用量成長。

- 晶圓極端薄化與背面製程導入,製程中需透過暫時鍵合提供結構支撐,承載晶圓需求同步增加。

整體而言,昇陽在再生晶圓領域具備高度市占地位,並深度參與台積電先進製程供應鏈,同時受惠於晶背供電導入下承載晶圓需求提升,為相關製程與材料需求成長的核心受益者之一。

天虹(6937.TW)

天虹科技為台灣首家具備半導體先進設備量產能力的本土設備商,產品涵蓋物理沉積(PVD)、原子層沉積(ALD),以及晶圓鍵合(Bonder)/解鍵合(Debonder)設備,主要應用於半導體與化合物半導體製程。 其中,ALD 被視為實現高精度背面金屬與介電層沉積的關鍵技術。其競爭優勢為台灣少數具備先進製程前端設備量產能力的本土供應商,核心競爭力來自紮實的研發能力,使其設備布局自物理氣相沉積、原子層沉積延伸至晶圓鍵合與解鍵合,形成相對完整的前端設備產品線,並能快速且精準回應客戶需求,維持平均一年推出一項新設備的節奏。

在 BSPDN 技術發展趨勢下,天虹科技可望受惠於:

- 先進製程前端設備國產化趨勢推進,作為台灣少數可直接提供先進製程前端設備的本土廠商

- 晶背供電導入下,製程中對暫時鍵合(Temporary Bonding)與解鍵合(Debonding)設備的需求同步增加,進一步擴大其相關設備的應用空間。

整體而言,天虹為台灣少數具備先進製程前端設備量產能力的本土設備供應商,產品涵蓋原子層沉積與物理氣相沉積設備,並深度參與先進製程與晶背供電相關製程,受惠於暫時鍵合與解鍵合設備需求提升,為先進製程設備國產化趨勢下的核心受益者之一。