隨著晶片製程正式邁入 2 奈米世代,蘋果下一代 A20 晶片將首度把台積電的 WMCM(Wafer-level Multi-Chip Module) 導入量產供應鏈。蘋果原本採用的 InFO 技術在 AP 之間的 I/O 數量存在限制,且 DRAM 在 InFO 的封裝下,已接近其效能極限,WMCM 的核心優勢在於能將 CPU、GPU 及高速記憶體等多個功能晶粒,直接在晶圓層級進行高密度的精密整合,使整體晶片效能提升。

這篇文章接下來將重點分析 WMCM 的核心概念與製程,並且和目前主流封裝如 InFO、CoWoS 等在架構與特性上的差異做出詳細比較。最後整理在材料、設備供應鏈中,哪些類型的廠商最可能成為 WMCM 擴產下的直接受惠者。

相關文章:台灣產業小學堂:CoWoS 介紹

WMCM 是什麼?

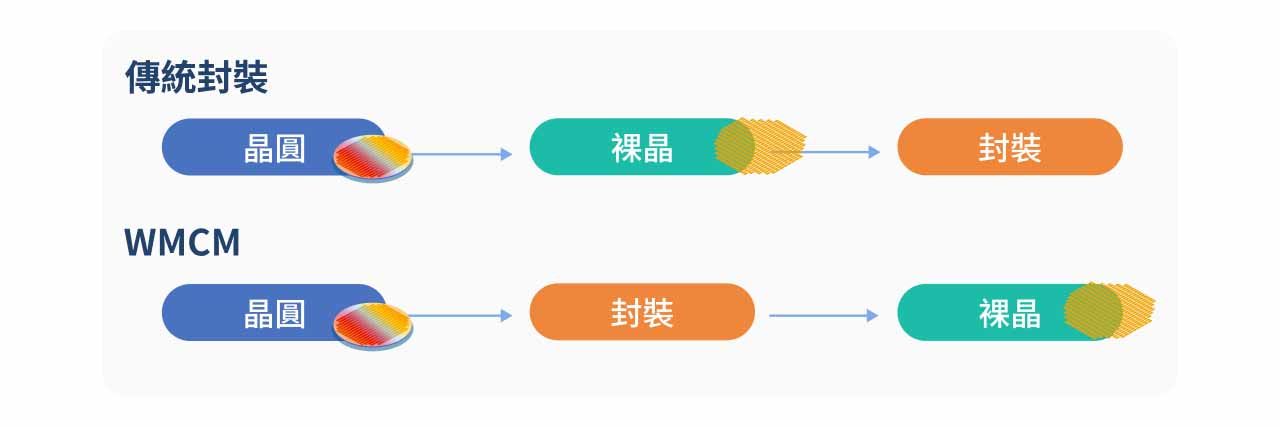

晶圓級多晶片模組(Wafer-Level Multi-Chip Module, WMCM)為台積電的一種先進封裝技術,被視為 InFO-PoP(整合型扇出型堆疊封裝)的進階版架構。 WMCM 與傳統單晶片封裝不同:後者通常先將晶圓切割成單一裸晶,再以載板封裝、焊接到印刷電路板;WMCM 的核心概念則是將封裝部分提前至晶圓階段完成,實質上是一種「晶圓級封裝與多裸晶異質整合的結合」。

![]()

WMCM 技術核心

WMCM 屬於 InFO(Integrated Fan-Out) 架構,與 CoWoS-R (Chip-on-Wafer-on-Substrate with RDL) 製程結構相似,特點在於其在晶圓階段就將多種裸晶(dies)如 AP 處理器、LPDDR 記憶體、被動元件等,在同一封裝結構中進行橫向整合成封裝模組,然後再切割為單一晶片。 但在封裝過程省略了 CoWoS 需要使用的基板(substrate)或矽中介層(silicon interposer),而是將晶片直接嵌入模塑樹脂材料(Molded Resin),並透過重佈線層(RDL, Redistribution Layer)直接在晶圓上進行裸晶間的互連與佈局,實現訊號水平傳輸。

與傳統封裝中 I/O 只能集中在裸晶下方的限制不同,Fan-Out 架構的核心在於,藉由 RDL 將訊號向外擴展,不僅能提升可連接的接腳數,也提供更多的空間讓 AP、記憶體等進行垂直堆疊或橫向整合,擴展連結性與封裝自由度。 因此 Fan-Out 技術能夠有效縮短晶片訊號路徑,降低系統功耗與延遲。

此外,WMCM 與 InFO-PoP 將記憶體直接堆疊在邏輯晶片上方不同。由於採用 2.5D 整合的方式,WMCM 是透過將邏輯晶片與 DRAM 進行平面封裝,取代上下堆疊的方式,裸晶可平行橫向並排。WMCM 更採用雙層結構,上層放置 AP 和記憶體,下層放置多顆電容。電容直接位於 AP 與記憶體下方,能降低雜訊並穩定電源電壓。 整合電容到同一封裝中,能夠更進一步地減少互連路徑長度並提升訊號傳輸效率,同時縮小整體尺寸。

綜合而言,WMCM 不僅能提升封裝的晶片數量,更因為不使用基板而改用 RDL ,因此製程更精簡,在封裝尺寸厚度、散熱效能、訊號損耗等都有所提升,能有效提升行動裝置的續航力,且由於省略了基板的使用,整體的成本結構相較於其他先進封裝技術低。這些優勢使其在手機、通訊晶片等空間敏感型產品中,成為不可或缺的封裝技術。

InFO 製程流程

InFO 製程流程涵蓋自玻璃載具處理至晶圓切割在內共九個主要步驟,其中以模塑封裝與重佈線層(RDL)技術為整體製程中最關鍵的核心環節。

詳細流程介紹

1. 玻璃載具(Glass Carrier)

作為後續製程的暫時性機械支撐,玻璃載具可在異質整合所需之薄晶圓製程中提供結構支撐,避免晶圓於後續加工過程中發生破裂或缺陷,以維持良率穩定。

2. 精密取放(Pick and Place)

逐顆選取完成前段製程的已知良品裸晶,依預先設計之封裝佈局精準放置於玻璃載板指定位置。 由於晶片位置將直接決定後續 RDL 走線、I/O 配置、電源與散熱設計,且完成模塑後無法再行校正,Pick and Place 為 InFO 製程中決定結構精度、翹曲控制與量產良率穩定性的關鍵基準。

3. 模塑封裝(Molding)

Molding 是先將固態或半固態的模塑材料均勻鋪放於晶片上方,再透模具在受控溫度與壓力下進行壓縮與固化,使樹脂流動並填滿晶片間隙,藉此降低氣泡產生、減少晶片位移風險,並確保晶圓的厚度分布一致。透過將晶片完整嵌入封裝樹脂(Molded Resin)中,將所有晶片「鎖定」在同一個機械結構內,建立後續製程所需的剛性與穩定性,避免晶片在後段製程中將因熱循環、機械震動或化學處理而產生位移、傾斜甚至破裂,使其能承受後續高應力、高精度的研磨、CMP 與多層 RDL 製程。

過去在封裝製程中,先需要用點膠頭將 underfill 底部填膠來填補晶片間距中的縫隙,再以 L-EMC 進行外部模封,但目前則面臨晶片間距縮窄,且製程道數大幅增加的問題。相關供應鏈中,目前長興(1717.TW)推出液態封裝 MUF 膠,可將底部填充與封模製程整合為單一步驟,不僅減少材料用量,也能縮短製程時間並提升良率。

4. 背面研磨(Back Grinding) / 化學機械平坦化(CMP)

Back Grinding 於晶圓正面貼附膠帶後,自背面移除多餘模塑材料與部分晶片厚度,使重組晶圓達到目標高度並維持厚度一致,流程分為快速降厚的粗磨與降低表面粗糙度、抑制微裂紋的細磨。 其後以 CMP 結合化學反應與機械拋光修復背面研磨所造成的損傷與應力,以降低後續製程中翹曲或碎裂風險。

5. RDL(Redistribution Layer)製程

- 塗佈(Coating):在晶圓表面旋塗聚亞醯胺(PI)、PBO 或其他介電材料,形成電氣絕緣層與機械緩衝層,並透過烘烤與固化控制膜厚、應力與附著性。

- 微影(Lithography):利用光阻塗佈、曝光與顯影,在介電層上精準定義金屬線路與通孔的幾何形貌。

- 濺鍍(Sputtering): 物理氣相沉積 (PVD) 技術的一種,在表面沉積一層極薄且均勻的金屬種子層,通常包含黏著層(如 Ti、Cr)與導電層,其功能在於提供後續電鍍的導電基礎並確保金屬與介電層之間的附著強度。

- 電鍍 (Plating):利用電解原理將金屬沉積到晶片或封裝基板上,用於形成 RDL、TSV等,以提升導電性、可靠性,並達成微縮化、高深寬比填充的目標。

- 蝕刻(Etching):當金屬線路達到規格後,會去除光阻並進行蝕刻,將未被電鍍覆蓋的多餘沉積層金屬選擇性移除,使 RDL 線路彼此電氣隔離且邊界清晰,最終形成完整且可重複堆疊的重佈線結構。

6. 載體分離(Carrier Debonding)

玻璃載板以臨時貼合方式作為製程支撐,並非產品結構的一部分;待上層 RDL 與相關結構完成後,透過加熱或溶劑軟化貼合層,將晶圓自載板分離,以利後續製程。

7. 植球(Ball Drop)

將尺寸、成分與位置皆高度受控的錫球,精準配置於晶片上已完成表面處理的焊墊位置,以建立後續與電路板之間的機械支撐與電氣連接。

8. 測試(Testing)

透過接腳進行電性、功能、溫度與壽命等測試,檢驗功耗、頻率與 I/O 表現,篩除缺陷或效能不足之晶片,以確保出廠前之可靠性與效能符合規範。

9. 晶圓切割(Singulation)

將完成製程與電性測試的晶圓沿切割道分離為單顆裸晶。隨著晶圓薄化、RDL 延伸至邊緣及大型裸晶與 Chiplet 架構導入,為降低邊緣崩裂與微裂紋風險,製程逐漸由傳統鑽石刀片切割轉向隱形雷射或電漿等非接觸式切割技術。

InFO-M 技術優勢

高密度 RDL 大幅縮短互連路徑改善高速訊號完整性並降低功耗

InFO-M 採用 3 層、2/2µm 線寬/線間距的高密度 RDL 佈線層,並且不需要額外的封裝基板與 TSV,封裝面積小於 500 mm²。 相較於 InFO-POP 包含 3 層 RDL 佈線層,佈線層間距為 2-10µm,佈線層間距更進一步地縮短。首先,高密度 RDL 直接在晶片重佈 I/O,使得晶片之間與晶片對外的互連路徑顯著縮短,訊號不需要經過基板的多層走線與 TSV 垂直導通結構。由於 RDL 線寬 / 線距可達到遠小於基板,互連阻抗、寄生電容與寄生電感明顯下降,高速訊號的串擾與功耗同步降低。

取消基板與 TSV 實現高密度多晶片整合

在封裝尺寸與系統整合密度上,取消基板與 TSV 代表整個封裝結構高度與橫向擴展都被有效壓縮。 對於封裝面積小於 500 mm² 的產品而言,InFO-M 在不導入中介層的情況下,透過多層高密度 RDL 實現多顆晶片或 chiplet 的緊密佈局,使系統整合密度大幅提高。對行動裝置、高效能但尺寸受限的 AI / HPC 邊緣運算晶片特別重要,因為封裝面積與厚度往往直接限制終端產品的設計與散熱配置。

以 RDL 為核心簡化製程與供應鏈

在成本結構與良率風險方面,不使用基板與 TSV 可顯著簡化整體供應鏈與製程複雜度。 高階 ABF 載板成本高、交期長,且在 I/O 數量增加、高層數下良率風險明顯;TSV 則涉及蝕刻、填銅、CMP 等高成本且良率敏感的製程。InFO-M 以 RDL 為核心,能避免上述高風險製程,在單位 I/O 成本與整體封裝成本上更具競爭力,也更適合大規模量產。

透過簡化封裝結構讓熱源更直接契合散熱路徑

在散熱管理方面,簡化的封裝結構有助於改善熱傳導路徑與應力分佈。InFO-M 封裝中,熱源可更直接與上方散熱結構耦合,減少基板與 TSV 所帶來的熱阻。 同時,少了異質材料層造成的熱膨脹係數(CTE)不匹配,對於長期熱循環可靠度、翹曲控制與微裂紋風險都有正面效果。

高密度 RDL 提供布線自由度,在效能、成本取得平衡

最後從擴展性來看,高密度 RDL 提供了比傳統基板更高的佈線自由度,使得系統設計更容易導入異質整合,同時又不必承擔 TSV 架構在尺寸放大時的成本與風險。 對於期望接近 chiplet 架構效益的產品而言,InFO-M 在效能、成本與量產可行性之間取得了一個相對平衡且具延展性的解決方案。

InFO-M 技術限制

雖然 InFO-M 透過高密度 RDL、去基板化與去 TSV 的封裝架構,在電性效能、封裝尺寸、成本結構、可靠度以及系統整合彈性方面展現出顯著優勢,但在實際量產與應用場景中,仍然存在一定程度的技術限制與挑戰。

以 RDL 取代基板所帶來的平面延展瓶頸

InFO-M 的最大限制來自於 RDL 取代基板所帶來的平面延展瓶頸。高密度 RDL 雖然線寬線距極小,但 RDL 層數有限、可承載總 I/O 數量仍受限於薄膜製程與翹曲控制能力。 當需要極高 I/O 時,RDL 層數快速增加會導致製程複雜度、良率損失與成本急遽上升,難以支援複雜晶片堆疊與高密度互連。

散熱能力仍不及 CoWoS

在功耗密度與散熱上限方面,InFO-M 雖然相較於 InFO-POP ,散熱表現提升了不少,但其散熱能力仍然低於 CoWoS,InFO-M 的模塑樹脂的導熱能力較差,並不適用於「極高功耗、長時間滿載」的 HPC 晶片。由於其核心仍是薄型 RDL 結構,缺乏如矽中介層或厚基板可作為熱擴散層,當單顆或多顆 die 的總功耗快速上升時,熱流密度會高度集中於局部區。換言之,InFO-M 更適合功耗較低、效能密度導向的設計,而非高功率應用的晶片。

然而,InFO-M 的劣勢並非技術缺陷,而是因其定位高度清晰導致;它並不是為了取代其他先進封裝技術,而是聚焦在「封裝面積中小、I/O 密度高、對電性與尺寸極度敏感、但功耗與系統規模可控」的應用。 一旦目標應用需極高 I/O 整合、高頻寬、極高功耗、或需要高度模組化的系統層級整合,InFO-M 的結構性限制便會開始顯現,此時 CoWoS 或其他 2.5D/3D 架構反而更具優勢。

InFO-M (WMCM) 與其他先進封裝比較

| 技術 | InFO-PoP | InFO-oS | InFO-L | InFO-M (WMCM) |

|---|---|---|---|---|

| 結構特點 | RDL+TIV,AP +DRAM 堆疊整合 | RDL+Substrate(含 TSV) | InFO-R+局部矽互連(LSI) | 高密度 RDL ,無Substrate 和 TSV,橫向整合 |

| RDL 線寬/線間距 | 2/2µm | 2/2µm | 0.4/0.4µm | 2/2µm |

| 優勢 | 降低封裝高度、縮小封裝體積 | 可整合多個邏輯晶片、支援更大封裝尺寸 | 密度最高,可整合多個邏輯晶片,用於 HPC。支援 SoC 混合焊盤間距 | 橫向整合、訊號水平傳輸,裝尺寸厚度、散熱效能、訊號損耗等都有所提升 |

| 終端應用 | Apple A 系列晶片 | Apple M Pro/Max CPU/Vision Pro。 | Apple M Ultra CPU | Apple A 系列晶片(A20 系列後) |

整體而言,InFO 系列皆以重佈線層為核心,但不同分支的設計取向差異明確;其中 WMCM 主打「高密度 RDL 的橫向整合」,在不使用基板與 TSV 的前提下完成多晶片互連,具備訊號傳輸效率與整體厚度控制的結構優勢,並可同時改善散熱效能與訊號損耗,因而被視為後續高階整合封裝的重要方向,終端應用以 Apple A 系列晶片為主,且預期自 A20 世代起成為關鍵導入方案。相較之下,InFO-PoP 以 RDL 搭配 TIV 與 AP、DRAM 堆疊整合為主,重點在降低封裝高度與體積;InFO-oS 則透過 RDL 與基板結合並導入 TSV,提升整合彈性以支援更大封裝尺寸,主要對應 Apple M Pro、M Max 等平台;InFO-L 以 InFO-R 搭配局部矽互連,提供更高密度互連能力,適用於需要多邏輯晶片整合的高效能運算情境。

WMCM 與 CoWoS 家族比較

| 技術 | CoWoS-S | CoWoS-R | CoWoS-L | WMCM |

|---|---|---|---|---|

| 封裝規格 | 2.5D | 2.5D | 2.5D | 2.5D |

| 製程流程 | Chip Last | Chip Last | Chip Last | Chip First |

| 中介層 | 矽中介層 + TSV | 矽中介層 + RDL | 局部矽互聯(LSI)+RDL | 無 (僅 RDL) |

| 黏晶 | 覆晶封裝/重流焊接、TCB | 覆晶封裝/重流焊接、TCB | 覆晶封裝/重流焊接、TCB | 覆晶封裝 |

| 成本 | 高 | 中 | 最高 | 最低 |

| 終端應用 | HPC、AI 加速器 | HPC、中高階 AI ASIC | HPC、大型訓練模型 | 行動裝置、消費性電子 |

| 主要產品 | NVIDIA Hopper GPU | AWS Trainium ASIC | NVIDIA Blackwell GPU | Apple Silicon |

WMCM 與 CoWoS 家族同屬 2.5D 封裝,但核心差異在於製程路徑與中介層架構:CoWoS-S/R/L 皆採 Chip Last 流程,需搭配中介層以提供高密度互連,其中 CoWoS-S 以矽中介層與 TSV 為主、CoWoS-R 以矽中介層結合 RDL、CoWoS-L 則導入局部矽互連與 RDL,在互連能力與系統規模上依序提升,但也同步推升成本,應用場景集中於 HPC 與 AI 加速器領域,對應產品包含 NVIDIA Hopper/Blackwell GPU 與 AWS Trainium 等中高階 AI ASIC。相較之下,WMCM 採 Chip First 流程,省略中介層結構、僅以 RDL 完成互連,並以覆晶封裝為主要形式,使其在材料與製程複雜度上顯著簡化、成本結構亦為四者中最低,因而更適合對體積、厚度與成本敏感的行動裝置與消費性電子,代表性終端產品為 Apple Silicon。

從 InFO 到 WMCM:技術演進及影響

目前智慧型手機晶片廣泛採用 InFO 技術(InFO_PoP 為主),主因在於其具備極薄的封裝優勢,並能透過 PoP 結構將記憶體與處理器直接堆疊以節省空間,然而,隨著 SoC 的 AI/NPU/GPU 長時間高負載更普遍、當 I/O 數提高、記憶體容量、頻寬上升,現行 InFO 開始面臨一系列問題,如高熱傳導受限於堆疊結構而引發的散熱瓶頸、封裝面積難以進一步擴大以容納更多小晶片、DRAM 配置往上堆帶來厚度和製程上的壓力等。

WMCM 作為 InFO 的下一階段解決方案,在晶圓級就把多顆 die 以更緊密方式整合,也具備更高密度的重佈線層,不只是互連更短,更能有效整合多顆異質晶片並優化散熱佈局,若 WMCM 穩定量產並放量,需求範圍可望由智慧型手機延伸到 MacBook 的 M 系列處理器,以及頭戴式裝置所採用的 R 系列晶片,此外,在進入 2 奈米世代並追求更強大的 AI 整合能力時,高通、聯發科的旗艦級晶片極有可能將原有的 InFO 方案升級為 WMCM 以突破效能極限,然而,市場估算 WMCM 單顆封裝成本約 3,000–4,000 美元、明顯高於 InFO 的 1,500–1,800 美元,意味著單位出貨所帶動的材料、設備投資強度都會同步拉高,在 WMCM 效能未被驗證前,導入時程恐怕受限。

| 項目 | InFO_PoP | WMCM |

|---|---|---|

| 封裝類型 | 扇出型晶圓級封裝 | 晶圓級多晶片模組 |

| 晶粒數量 | 1 顆 | 2–4 顆 |

| 堆疊方式 | 垂直堆疊,PoP(Package on Package) | 水平配置(side-by-side) |

| 製程 | 3nm、5nm | ~2nm |

| RDL 層 | 1–2 層,用於簡單 I/O 重新配線 | 2–3 層,支援多晶粒互連 |

| 目標功率 | 3-10W | 5-25W |

| 晶片體積 | 大 | 小 |

| 封裝厚度 | 隨記憶體堆疊增加而變厚 | 更厚,但厚度控制更佳 |

| 散熱表現 | 隨堆疊層數增加而面臨挑戰 | 散熱能力提升 |

| 成本 | 低 | 高,但低於 CoWoS |

| 量產狀態 | 自 2016 年起 | 1H26 |

受惠台灣廠商

志聖 (2467.TW)

公司簡介

志聖 (2467.TW) 成立於 1966 年,專注於開發先進封裝及 IC 載板所需的關鍵製程設備,包括壓合、貼合、剝離、烘烤,以及電鍍前預處理的濕製程技術。其產品主要應用於 PCB、FPD、半導體、先進封裝多種業。

志聖生廠區包含台北、台中、中國廣州、昆山等地。現有的半導體客戶包括台積電(2330.TW)、日月光(3711.TW),PCB 領域包含欣興(3037.TW)、滬電股份(002463.SZ)、勝宏科技(300476.SZ)等,皆為全球領導廠商。

成長動能一:台積電推動先進封裝設備在地化,志聖大客戶占比可望持續提升

根據台積電 ESG 年報,2030年台積電目標在地採購比例是原物料 50%、零配件 68%、後段設備 38%比率,因其能提供比海外廠商更即時的支援,目前台系廠商後段設備市佔率僅 10%,尚有 3~4 倍提升空間。此外,2020 年,志聖與均豪、均華組成 G2C+聯盟,推動台灣先進封裝設備在地化,預期將持續受惠資本支出在地化,這點從志聖來自台灣客戶的營收比例逐年遞增就能看出,主要由台積電及日月光先進封裝擴產計畫拉動。

除先進封裝外,PCB 部分,由於 AI 需求強勁,推動 PCB 廠增加資本支出,目前主要廠商如臻鼎、欣興、金像電、勝宏科技等,皆在今年與明年大幅提高資本支出,此外,為因應去中化趨勢,生益電子、定穎投控、欣興、勝宏科技等投投皆前往東南亞擴廠,預期將推升相關 PCB 設備需求。

成長動能二:志聖提供黃光製程加熱設備與後段工業烤箱切入 WMCM 供應鏈

回到 WMCM,在 WMCM 封裝中,志聖將提供黃光製程加熱設備,該設備用於晶圓級封裝中,針對光阻劑或介電層進行精確的加熱與烘烤處理,確保黃光微影製程的穩定性。因為 WMCM 技術需要連接多顆晶片 RDL 層將顯著高於 InFO 封裝,而 RDL 層數越多,固化次數需求也將同步提升,黃光製程加熱設備設備稼動時間將拉高,並同步提升設備需求。

此外,WMCM 製程中會使用大量不同的材料,在加熱與冷卻的過程中,不同材料的膨脹係數(CTE)差異,極易導致晶圓發生翹曲與應力問題,而隨著 WMCM 的 RDL 層數增加,介電層、金屬層與光刻循環次數同步上升,晶圓經歷的熱循環與層間應力疊加更頻繁,使翹曲、對位失準與良率風險進一步放大。 志聖的黃光製程加熱設備能提供極高精度的恆溫環境與受控升降溫曲線,能確保晶圓在多層佈線與加熱過程中保持平整。 WMCM 設備單價與 CoWoS 相當,市場預期相關設備占志聖 2026年營收將達中個位數。

後端封裝部分,由於 WMCM 採用了 MUF(Molding Underfill) 技術,這是一種將底膠與模封材料合二為一的製程,能簡化步驟並提升散熱。在膠材注入後,需要透過精密的工業烤箱進行長時間的後固化處理,使封裝材料達到預期的機械強度與熱穩定性。而志聖具備工業烤箱產品,有望打入後段封裝製程,形成潛在利多。

長興 (1717.TW)

公司簡介

長興(1717.TW)成立於 1964 年,是全球領先的合成樹脂與電子化學材料供應商。其核心業務以材料化學為核心,主要事業橫跨合成樹脂、電子材料與特用材料三大領域,產品廣泛應用於 PCB、汽車、建築塗料、3C家電等領域。

長興的生產基地遍布全球,涵蓋台灣、中國、美國、日本、泰國等。憑藉深厚的技術基底,長興已成為蘋果的材料供應商,並成功獲得台積電先進封裝材料訂單,同時服務於全球各大電子、通訊及製造業大型企業。

底部填充為晶片封裝中關鍵製程

底部填充(Underfill)是在倒裝晶片(Flip Chip)封裝中用來提升可靠性的關鍵製程。由於晶片與基板的 CTE 不同,溫度循環會在焊球處產生應力、提高焊點斷裂風險,而底部填充藉由把材料填入焊球間隙,可分散應力、增加機械強度,同時也能在一定程度上改善散熱與防潮抗腐蝕,延長壽命。現行主流底部填充路線包括毛細底部填充(CUF)與模塑底部填充(MUF)。

CUF 提供高可靠性及低風險,惟製程節拍慢、效率受限

CUF(Capillary Underfill)屬於後填充,在回流焊或鍵合完成後,先在晶片邊緣點膠(多為環氧樹脂),再靠毛細作用讓液態膠自動流入晶片與基板之間並充滿焊球間隙,最後再加熱固化形成保護層。CUF的優勢在於可靠性高、填充相對均勻、空洞風險較低,常見於高階 CPU/GPU 等傳統倒裝封裝以及智慧手機 AP、HPC 等重視可靠度的應用。然而,CUF 需要逐顆點膠與等待流動、固化,整體產出速度較慢,同時,若助焊劑殘留清洗不佳,可能影響填充品質。

MUF 一體化轉移模塑較 CUF 契合 WMCM 製程

MUF(Molded Underfill)則是一體化封裝,晶片貼裝後,直接以環氧塑封料(EMC) 透過轉移模塑注入模腔,在塑封成型的同時完成底部填充與晶片保護,最後固化形成完整封裝結構。相較 CUF,MUF 可大幅縮短生產循環時間、降低設備成本,並減少一次高溫熱處理所帶來的製程風險。此外,隨製程進入 2 奈米、錫球間距持續縮小,CUF 僅靠毛細作用更難完全填滿微小空隙而易產生氣泡,MUF 則能藉由模壓強制填充、降低空洞風險並提升量產良率,因此更貼近 WMCM 的高密度、薄型化與放量需求。材料面上,CUF 與外層 Molding 若使用不同材料,兩者 CTE 不一致容易在大面積封裝引發嚴重晶圓翹曲,而 MUF 內外材料一致,使結構應力分佈更均勻,對 WMCM 這類 12 吋晶圓級的大面積封裝特別有利,可更有效維持平面度並提升良率。

長興憑藉低翹曲、高附著 EMC 的 MUF 產品打入台積電先進封裝供應鏈

WMCM 採用 MUF 技術,其製程挑戰主要集中在填充均勻性與材料、應力控制。由於 MUF 的模塑流動更敏感,較可能出現空洞或局部未填滿區域,EMC 需同時兼具低黏度與高流動性,且為了進入微小間隙,填料粒徑需進一步縮小,此外,EMC 與晶片、基板的熱膨脹係數 CTE 若不匹配,可能導致熱應力累積與翹曲問題。而長興憑藉材料低翹曲、對 Si 晶片和 Cu 介面優異的附著能力,成功分食日系廠商 Namics、Nagase 市佔,取得台積電先進封裝材料訂單,供應蘋果新款 iPhone 與 Mac 處理器所需的 MUF 材料,截至 3Q25,MUF 占整體營收僅 0.3~0.4%, 長興預計晶圓級液態封裝材料逐步於 2Q26~3Q26 放量,屆時 2026~2027 年占比可達到 5%。