Intel 在過去數年間歷經技術推進受阻、關鍵決策失誤與競爭對手夾擊,從曾經製程領先的產業霸主地位迅速滑落,不僅錯失 AI 算力爆發的關鍵黃金期,更因此陷入財務虧損擴大與市佔率持續流失的困境,一度面臨分拆重組與企業存續能力備受質疑的嚴峻考驗。然而,隨著 Intel 於 CES 展出 Panther Lake 處理器並揭示 18A 製程的最新進展,公司在先進製程與產品路線上逐步展現實質突破,18A 能否成為帶領 Intel 重返產業競爭核心、重塑長期競爭力的關鍵轉折,成為市場高度關注焦點。

18A 製程介紹

製程定位與戰略意義

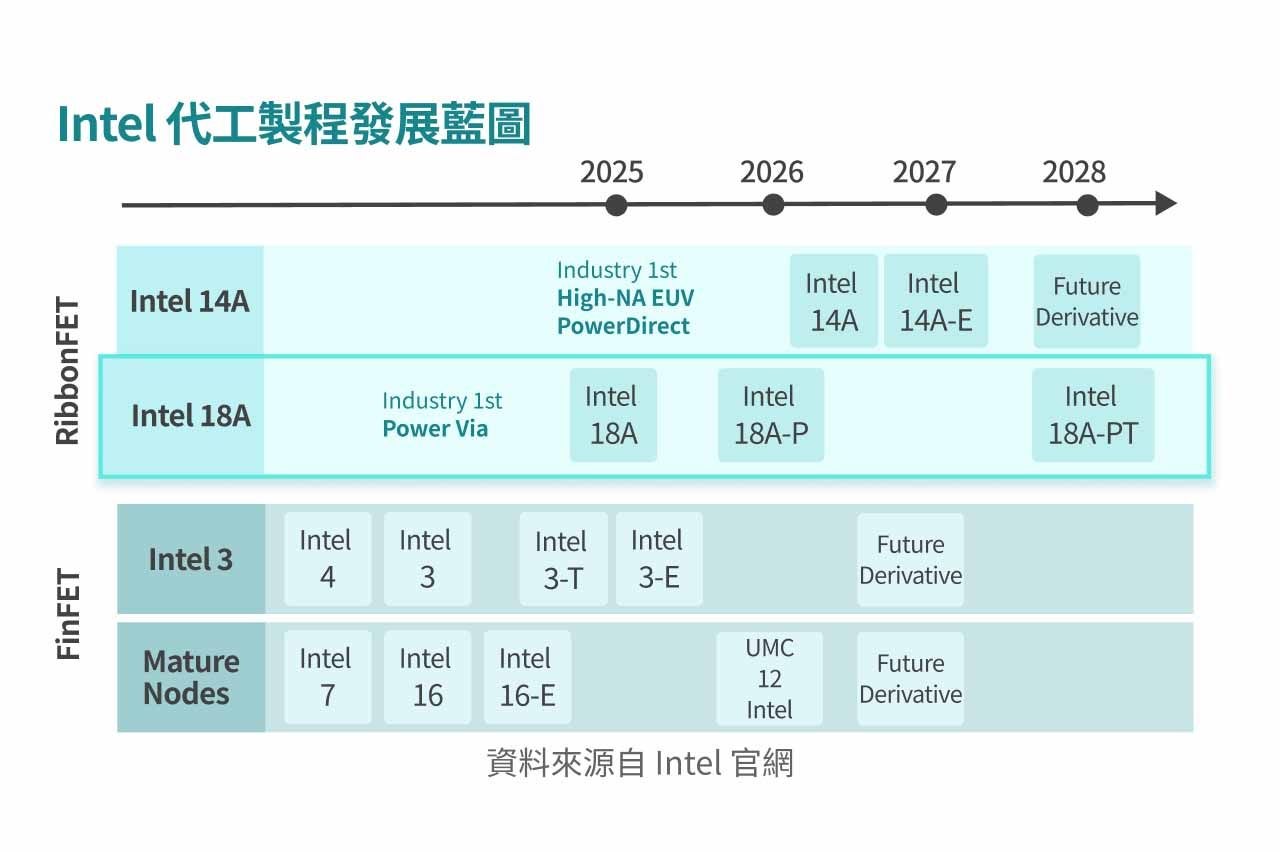

Intel 18A 在 Intel 製程藍圖中扮演關鍵角色,是 Intel 重返先進製程領導者地位的核心節點,透過 18A 製程,Intel 不僅試圖在自有產品線上重建製程優勢,也明確將其定位為代工服務(Intel Foundry Services, IFS)的旗艦節點,直接對標台積電(TSMC)於先進製程市場的領先地位。 18A 導入多項關鍵技術創新,包括 PowerVia 背面供電架構與 RibbonFET(GAA)電晶體設計,預期將在效能、功耗與面積等 PPA 指標上實現顯著提升,從 Intel 的規劃來看,18A 將成為北美最早具備量產能力的次 2 奈米級先進製程節點之一,對於希望分散供應鏈風險、並在美國本土生產先進晶片的客戶而言,具備高度戰略吸引力。

18A 技術細節

RibbonFET(GAA 環繞式閘極電晶體)

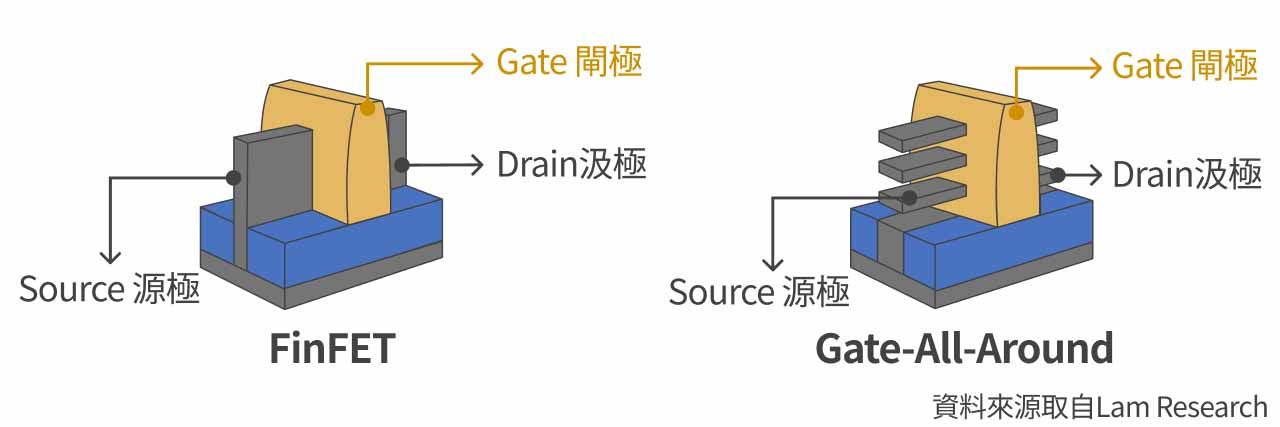

隨著晶片越做越小,FinFET (鰭式電晶體)已經達到了物理極限,難以再微縮且漏電嚴重,像 RibbonFET 這種環繞式閘極電晶體(Gate-All-Around,GAA) 是摩爾定律得以延續的關鍵,它是半導體產業中的一項重大革命,旨在取代過去十多年來主流的 FinFET架構,使晶片能進一步微縮至 2 奈米及更先進的製程,環繞式閘極電晶體就像是把電晶體的導電通道從直立的魚鰭變成了水平堆疊的絲帶,並讓控制開關的閘極完全包裹住這些絲帶,這對未來 AI 運算和高效能資料中心至關重要。雖然這種最先進的電晶體統稱為 GAA 技術,但各大廠的命名不同,而 RibbonFET 是 Intel 對於其 GAA 電晶體架構的稱呼,三星將其稱為 MBCFET (Multi-Bridge Channel FET),已在 3 奈米製程率先量產,台積電則統稱為 GAAFET。

PowerVia(BSPDN 背面供電技術)

傳統正面供電架構中電源與訊號線路高度混合,不僅造成金屬層擁塞、也使電阻與電壓下陷問題日益嚴重,進而影響整體效能與能耗表現,為解決此一問題,Intel 推出業界首創的 PowerVia 背面供電網路(BSPDN),成為 18A 製程世代的核心技術之一。PowerVia 的設計核心在於將電源供應網路由晶片正面完全移至背面,並在標準單元中導入奈米級穿孔(Nano-TSVs),使電力能以更直接、低阻抗的方式輸送至電晶體,透過電源與訊號線路的徹底分離,釋放正面金屬層空間能改善佈線壅塞並提升設計彈性,同時大幅減少電壓下陷(Voltage Droop)。

在效能表現上,PowerVia 可使標準單元使用率提升約 5% 至 10%,並帶來最高約 4% 的 ISO 電源效率提升;此外,由於前段金屬層 RC 效能改善約 12%,加上穿孔電阻降低最多可達 49%,整體電源完整性明顯優於過往架構;在邏輯庫配置方面,Intel 18A 提供 180CH 高效能版與 160CH 高密度版,以兼顧不同應用需求。這項技術 Intel 採取了領先業界的策略,先在 Intel 3 製程上開發 PowerVia 測試晶片並取得成功,這使 18A 在量產這項革新技術時具備更高的成熟度。

微影技術

在微影技術方面,Intel 18A 製程的成功關鍵在於其對 High-NA EUV(高數值孔徑極紫外光) 設備的先行部署。 身為 ASML 該設備的首波客戶,Intel 在 18A 研發階段便積累了關鍵的曝光參數與設計規則,這為其後續 14A 的全面領先奠定了物理基礎。儘管 18A 在初期量產階段為了兼顧產能與成本,會採取標準 0.33 NA EUV 多重曝光與 High-NA 設備並行的靈活策略,但率先掌握 High-NA 技術讓 Intel 在 2 奈米以下的微縮競賽中,相較同業擁有更長的設備磨合經驗與技術數據,這對於實現更精細的電路圖案與減少製程步驟具有決定性意義。

Omni MIM 電容器應用 (非 18A 獨有)

在追求高效能運算的過程中,感應式功率下降一直是維持電壓穩定的主要挑戰,因此 Intel 在 18A 製程進一步導入了新一代高密度金屬-絕緣體-金屬(MIM)電容器,這些微型電容器廣泛分佈在電路層中,扮演著關鍵的儲能與平衡角色,能在電流急劇波動時提供即時緩衝,大幅抵銷功率波動,進而提升晶片在高負載下的運作穩定性,這種對電力穩定度的極致追求,是維持 2 奈米等級精密電路正常運作的核心基礎,確保供給電晶體的電力平穩且無雜訊干擾,對於生成式 AI 等現代工作負載而言至關重要,因為 AI 運算往往具有極高的突發強度,需要極其精準且即時的電力緩衝來確保系統不間斷運作、讓電力傳輸更加純淨。

先進封裝與 3D 晶片堆疊技術 Foveros (非 18A 獨有)

先進封裝已成為延續摩爾定律、提升運算效能的關鍵技術,而英特爾的 Foveros 3D 封裝技術,透過垂直堆疊方式,將多個具備不同功能的晶片模組整合至單一系統級晶片(SoC)中,大幅提升設計彈性與擴充性。 進一步結合 PowerVia 以及 EMIB 等技術,Foveros 建構出高度整合的異質封裝平台,使晶片能在有限的封裝空間內釋放更高的運算效能與頻寬潛力。值得注意的是,目前台積電與三星亦已推出各自的 3D 封裝解決方案,因此對英特爾而言,Foveros 雖是核心技術之一,但並非獨占或領先同業的製程門檻。

18A 製程應用

18A 的實戰價值將由 2026 年上半年的 Clearwater Forest (Xeon 6+ 處理器) 正式啟動,該處理器不僅擁有 288 個高效率核心,更透過 PowerVia 與 Foveros 實現了異質整合的極致,預期 IPC 較前代提升 17%。隨後的消費級 Panther Lake 處理器則將驗證 18A 在行動端的高能效表現,這些產品不僅是 Intel 自家產品線的重生,更是向代工客戶展示其能在美國本土實現次 2 奈米級穩定產出的旗艦標竿。

市場競爭:其他晶圓廠的發展藍圖

除 Intel 在先進製程上出現突破外,台積電與 Samsung 亦已在 2nm 製程上取得實質性進展,兩家公司皆於 2025 年啟動量產,顯示先進製程競賽為多方並進、節點密集推進的全面競爭格局。

台積電

台積電 N2 製程於 3Q25 啟動量產,並將逐步推出 N2 系列,提供客戶橫跨消費性電子、企業運算與 AI 應用等多元場景的產品選擇:其中 N2 主要適用於行動裝置與穿戴式設備,N2P 則在效能提升與功耗降低方面進一步優化,設計重心聚焦於旗艦級智慧型手機與高效能筆電;至於 A16 節點預期將整合更先進的封裝技術,鎖定高效能運算與雲端 AI 等具高度可擴展性的架構應用。

| 效能 | 功耗 | 晶片密度 | 量產時間 | 應用 | |

|---|---|---|---|---|---|

| N2 (vs N3E) | 提升 10-15% | 降低 25-30% | 提升 15% | 3Q25 | 行動裝置 |

| N2P (vs N2) | 提升 5-10% | 降低 5-10% | 與 N2 相同 | 2H26 | 智慧型手機 |

| N2X (vs N2) | 提升 5-10% | - | - | 2027 | - |

| A16 (vs N2P) | 提升 8-10% | 降低 15-20% | 提升 7-10% | 2H26 | 高效能運算 |

Samsung

Samsung 的 2nm 製程命名為 SF2,2025 年進入量產,初期聚焦於行動處理器晶圓生產,首項導入產品為自家 Exynos 2600 晶片;其後於 2026 年延伸發展為 SF2P 製程技術,效能較前一代提升約 12%,功耗降低約 25%,市場傳出 Tesla AI6 晶片有望採用 SF2P 投片生產。同年 Samsung 亦同步規劃推出鎖定高效能運算與人工智慧應用的 SF2X 製程;至於 SF2A 製程則以車用處理器為主要應用方向,預計於 2027 年正式進入量產階段。

Intel 與 Samsung、台積電 2nm 製程比較

| Intel | 台積電 | Samsung | |

|---|---|---|---|

| 製程名稱 | 18A | N2 | SF2 |

| GAA 架構 | RibbonFET | Nanosheet | MBCFET |

| 晶背供電技術 | 已導入 (PowerVia) | A16 導入 (Super Power Rail) | 2027 導入 (類似 PowerVia) |

| 效能 | 提升 25% (vs Intel 3) | 提升 10-15% (vs N3E) | 提升 5% (vs SF3) |

| 功耗 | 降低 36% (vs Intel 3) | 降低 25-30% (vs N3E) | 降低 25% (vs SF3) |

| 良率 | 50% | 約 90% | 50% |

| 量產時間 | 2H25 | 3Q25 | 2025 |

| 策略重點 | 技術大幅革新,爭取製程領先 | Roadmap 穩定推進,確保良率與客戶需求 | 克服良率挑戰,擴大客戶基礎 |

| 優勢 | 首先導入晶背供電技術,供電與密度優勢顯著 | 技術成熟度高、生態系完整 | 較早導入 GAA 架構,具降低成本潛力 |

| 潛在挑戰 | PowerVia 量產成熟度及整合風險 | - | 良率爬升速度、市場競爭壓力 |

| 採用客戶 | 自家 Panther Lake 處理器 | 聯發科、QCOM、AAPL 等 | 自家 Exynos 2600 晶片 |

Intel 18A 以 RibbonFET 搭配 PowerVia 晶背供電作為主要差異化,相較 Intel 3 可帶來約 25% 效能提升與 36% 功耗降低,並試圖以供電效率與電晶體密度優勢重奪製程領先地位。 然而,從量產節奏與製造成熟度觀察,Samsung SF2 已於 2025 年率先量產,台積電 N2 亦於 3Q25 進入量產,時程皆早於 Intel 18A 規劃的 2H25;其中,台積電 N2 在良率表現與整體效能上均明顯領先 18A,顯示其技術成熟度與生態系優勢具備較高確定性,且已獲得多家一線客戶訂單肯定。相較之下,Samsung 雖具備較早導入 GAA 架構的經驗並主打成本潛力,但現階段仍須克服良率爬升速度與激烈市場競爭的雙重挑戰。 整體而言,Intel 18A 的關鍵勝負仍在於 PowerVia 於量產階段的整合成效與良率提升速度,唯有順利跨越量產成熟度風險,才能在先進節點競局中實質縮小與台積電、Samsung 的差距,並重塑長期競爭力。

市場看法與展望

18A 製程為 Intel 代工業務的關鍵節點,亦是市場高度關注的核心焦點。 近年來 Intel 在 PC CPU 市場承受顯著競爭壓力,主因在於 AMD 借助台積電先進製程,在效能與功耗表現上持續拉開差距;受限於自有製程推進落後,Intel 過去主流的 Raptor Lake 仍停留在 10 奈米節點,產品競爭力明顯不足,迫使公司於 Lunar Lake 與 Arrow Lake 世代大幅轉向台積電代工以維持產品表現。Panther Lake 則標誌策略上的重要轉折,作為首款基於 Intel 18A 製程的大規模量產晶片,相較前代展現顯著技術突破,官方數據顯示其效能較 Lunar Lake 提升約 60%,遊戲效能更大幅成長約 77%。

對 Intel 而言,Panther Lake 不僅是產品世代更新,更攸關其代工業務能否實現長期且可持續經營,其量產穩定性與能效表現將直接影響潛在客戶的導入意願,包括聯發科與 Qualcomm 等設計商皆持續關注其實際量產成果。 市場亦傳出 Broadcom 可能將部分 ASIC 需求分配至 Intel 18A-P 製程,Apple 亦正評估於 2027 年 M 系列晶片導入效能優化版的 Intel 18A-P;若 Panther Lake 能順利驗證製程成熟度與能效競爭力,Intel 爭取關鍵一線客戶的成功機率將顯著提升。在台積電先進製程產能長期吃緊的結構性背景下,18A 乃至後續的 14A 製程,具備成為潛在重要替代方案的戰略價值。

總結:技術突破與量產執行的關鍵時刻

整體而言,Intel 18A 不僅是一個製程節點的推進,更是 Intel 技術路線、代工戰略與長期競爭力能否重塑的關鍵。 18A 透過 RibbonFET 與 PowerVia 的同步導入,在電晶體架構與供電方式上實現跨世代革新,使 Intel 在技術設計層面重新具備與台積電、Samsung 正面競逐次 2nm 世代的能力。然而,從產業現實面觀察,台積電 N2 以更高良率與成熟生態系率先量產,Samsung 亦搶先卡位行動與特定應用市場,顯示先進製程競爭已轉為「量產執行力與客戶信任」的全面比拚。

對 Intel 而言,Panther Lake 與 Clearwater Forest 的量產表現,將直接決定 18A 是否僅止於技術展示,抑或真正轉化為可規模化的代工節點;若能成功驗證良率、能效與交付穩定度,18A 乃至後續 14A 將有機會在台積電產能長期吃緊的結構下,成為一線客戶的實質替代選項。反之,若量產成熟度不如預期,Intel 在先進製程競局中的追趕時間窗將進一步收斂。最終,18A 的成敗不僅關乎 Intel 代工業務,更將左右全球先進製程供應格局是否出現真正的多極化。