在當前 AI 產業的熱潮之中,由於晶片能帶來算力,進而驅動對模型及相關應用的擴展,這使得企業對先進半導體技術的需求逐步增加。如同我們在 CoWoS 介紹中所提到的,在未來除了持續降低「閘極長度」外,也可以藉由「先進封裝」來增加晶片效能。今天我們就讓 fiisual 來帶你看看,究竟什麼是 SoIC 封裝,以及在未來可能有什麼應用吧!

SoIC 封裝是什麼?

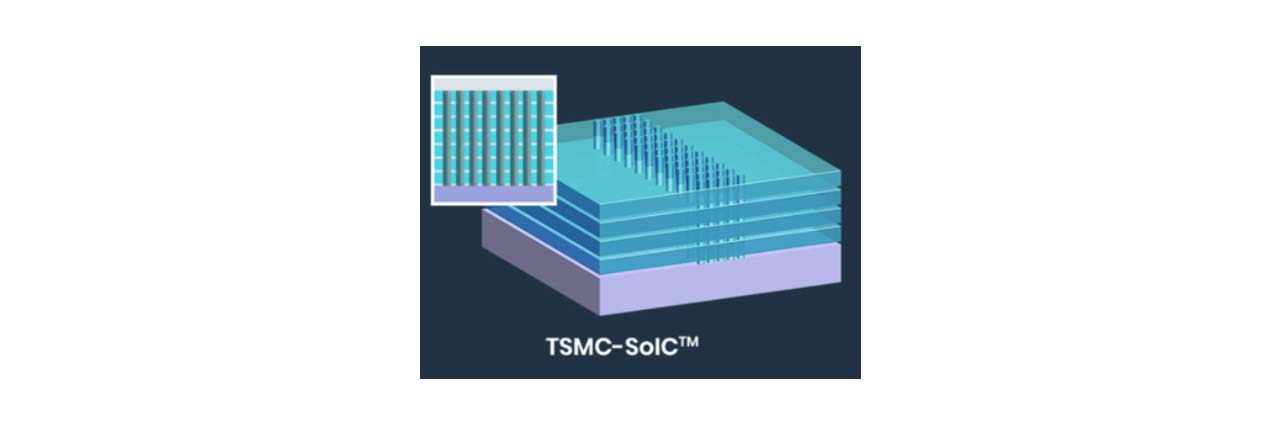

SoIC(System-on-Integrated-Chips)是一種由台積電(TSMC)開發的先進封裝技術,專注於高密度的 3D 晶片堆疊。先前我們提到 CoWoS 可以歸類在「2.5D」封裝,也就是在下層將 PCB 板和中介板以垂直的方式疊合 (3D),上層的 SoC 晶片和 HBM 則以水平的方式排列 (2D),因此綜合稱為2.5D。

SoIC 是業界第一個高密度 3D 小晶片堆疊技術,其特別之處在於使用矽穿孔(TSV)取代傳統金屬端點堆疊的方式,在晶片上以化學蝕刻或雷射的方式鑽孔,把所有晶片垂直堆疊在一起。這樣的方式可以減少矽中介板的使用,進而縮小整體堆疊體積。

| CoWoS | SoIC | |

|---|---|---|

| 英文全名 | Chip-on-Wafer-on-Substrate | System-on-Integrated-Chips |

| 封裝技術 | 2.5D | 3D |

| 目前使用情形 | 已經正式應用於產品中 | 目前仍在測試即持續研發中 |

不過因為要在晶片內直接製作矽穿孔的難度極高,此外,晶片與晶片或是晶圓與晶圓之間需要保持平整才能完全接合,此項技術的可靠度與良率仍有待提升,目前仍在測試和研發階段。

SoIC 的技術特點

高密度堆疊

SoIC 技術未來的目標是達到每平方毫米 100 萬個互連。封裝堆疊技術提高,可以實現更高的計算能力和更快的數據傳輸速率,並縮小了整體的封裝尺寸,整體而言也可以因訊號傳送的距離縮短而減少功耗。

無凸點設計

SoIC 的設計不使用傳統的凸點(bumps),而是採用混合鍵合(Hybrid Bonding)技術,這使得晶片之間的連接更加緊密,並且能有效提升散熱性能。混合鍵合技術允許晶片之間直接進行銅對銅 (Cu-Cu) 的連接,無需使用凸點作為連接。這種方法使得晶片之間的連接更加緊密,可以實現更高的互連密度。

目前 SoIC 有提供兩個不同的堆疊方案來滿足不同的場景使用需求:

1. SoIC - P

使用微凸點的方式堆疊,適用於對成本敏感的產品,例如行動裝置。

2. SoIC - X

使用無凸點的方式堆疊,適用於追求高效能運算的產品,可大量運用在人工智能相關的應用中。

多樣化應用

SoIC 技術適用於 10 奈米及以下的先進製程,並在雲計算、邊緣計算和高性能計算(HPC)等領域具有廣泛的應用潛力。舉例來說,SoIC 技術可以提升計算效率和數據頻寬,支持雲計算中對高性能和低延遲的需求。另外,SoIC 技術的高密度互連和低功耗特性也非常適合於邊緣計算應用,這包括自動駕駛汽車、增強現實和虛擬現實等需要快速響應的應用。

市場前景

隨著半導體技術的發展,SoIC技術被認為是未來晶片設計和製造的重要趨勢。台積電計劃在 2025 年開始量產這項技術,並預期將在多個高需求領域中發揮關鍵作用,如自動駕駛汽車和 AI 伺服器。總的來說,SoIC 技術代表了晶片封裝技術的一次重大進步,能夠在保持小型化的同時,顯著提升性能和效率。

雖然目前SoIC技術尚未發展成熟,仍處小量試產的階段,但各個美國大廠已逐步與台積電商討合作專案。其中AMD的MI300系列 AI GPU 和高階遊戲 CPU,以及蘋果的 M5 晶片皆傳出將在 2025 年跟進 SoIC 封裝。目前 SoIC 月產能大約為 4 千片,預計明年將至少擴大一倍,而 2026 年產能將數倍以上成長。

相信聰明的你已經完全了解 SoIC 封裝技術是什麼了,還想看其他AI產業相關的文章了話,不要錯過以下啦!